Principle

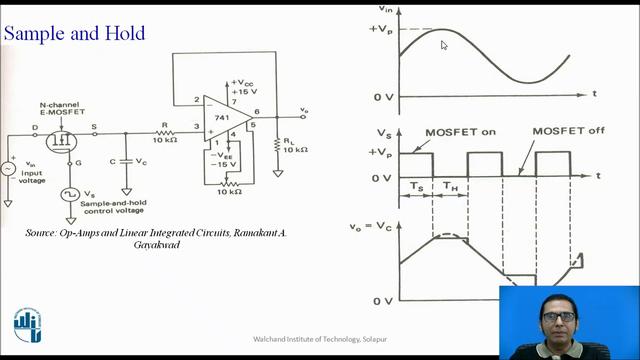

The sample-and-hold circuit can track or maintain the level value of the input analog signal. Under ideal conditions, when in the sampling state, the output signal of the sample-and-hold circuit changes with the change of the input signal; when in the hold state, the output signal of the sample-and-hold circuit is maintained at the input signal level value at the moment of receiving the hold command . When the circuit is in the sampling state, the switch is turned on, and the capacitor is charged at this time. If the value of the capacitor is small, the capacitor can be charged and discharged in a short time. At this time, the output signal of the output terminal changes with the change of the input signal; When the switch is in the hold state, the switch is off. This is because the switch is off and the input end of the integrated op amp is in a high-impedance state. The capacitor discharges slowly. Since one end of the capacitor is connected to a signal follower circuit composed of an integrated op amp, the output signal is basically maintained Is the signal level value at the moment of disconnection.

Basic model of sample and hold circuit

Technical indicators

Sample and hold circuit has two types: sample and hold These two working states have a great influence on the performance of the circuit and the performance of the entire A/D conversion part. In these two different modes, the characteristics of the circuit also have certain differences. The main technical indicators are analyzed according to the two different working states of the sample-and-hold circuit.

1) Main technical indicators in sampling state

Offset voltage refers to the output voltage value at the output terminal when the input terminal voltage is zero in the sampling mode. In order to ensure that the A/D conversion chip can accurately sample, the value of the offset voltage should satisfy the formula (1)

-the maximum change frequency, which refers to the highest change frequency of the output voltage in the sampling mode. This frequency value is affected by the capacitance of the holding capacitor and has a certain limit on the operating frequency of the system.

2) Main technical indicators in the hold state

The step-down rate refers to the rate at which the output voltage value of the output terminal changes with the input time in the hold mode. The step-down rate satisfies the formula (2)

-feedthrough attenuation, which refers to the decrease in the voltage value of the input signal when it is output at the output terminal after passing through the sample-and-hold circuit in the hold mode. In order to enable the A/D chip to accurately sample the signal, the feedthrough attenuation is less than 1/2 of the least significant bit LSB of the A/D chip.

3) Main technical indicators during state transition

Sampling time refers to the maximum time required to obtain the voltage value of the input signal when the circuit is switched from the holding state to the sampling state. Aperture delay refers to the time from the charging of the capacitor to the voltage stabilization when the circuit changes from the sampling state to the holding state. Aperture delay is a very important technical indicator, which directly affects the sampling rate and accuracy.

4) The main factors affecting the performance of the sample-and-hold circuit

A simplified sample-and-hold circuit model is shown in the figure

Simplified sample-and-hold circuit model

p>It can be seen from the simplified sampling circuit model that a sample-and-hold circuit is composed of input and output ports, switching switches, and holding capacitors. Therefore, the impact on its performance is mainly reflected in the following aspects: First, maintain the capacitance of the capacitor. The holding capacitance value of the sample and hold circuit should be considered comprehensively according to the actual application. If the capacitance value is small, the charging time of the capacitor during the sampling process will be short, and the signal with high change frequency can be better tracked, and the maximum change frequency of the main technical indicators mentioned above under the sampling state is very good. Improve. However, a smaller capacitance value will cause the circuit to discharge faster in the hold state, which will increase the voltage drop rate in the hold state, thereby affecting the sampling accuracy of the system. Therefore, in the actual design process, it is necessary to combine the system requirements to simulate and optimize the capacitance value of the holding capacitor to achieve the best effect. Input and output resistance value. The influence of the resistance value of the input and output terminals on the circuit performance is the same as the influence of the capacitance value of the holding capacitor, both of which are considered based on the length of the charging and discharging time of the circuit. Under normal circumstances, we hope that the smaller the resistance value of the input terminal, the better, so that the capacitor can be charged faster in the sampling state; we also hope that the larger the resistance value connected to the output terminal, the better, so that the switch is disconnected and the circuit enters the hold state. The system discharges slowly, and then the voltage reduction rate is reduced, which improves the sampling accuracy of the system. Sample and hold status switch. The performance of the switch also has a very important impact on the entire circuit. The turn-on and turn-off speed of the switch directly affects the accuracy of the sample-and-hold circuit. If the switching speed of the switch is slow, the circuit cannot switch to the sampling or holding state in the required time, and thus cannot meet the requirements of the system for sampling the received signal, causing the sampled signal to be distorted. In addition, the switch itself also has aperture delay and aperture jitter, all of which have a certain impact on circuit performance. Combined with the above analysis, when designing a sample-and-hold circuit, a signal follower composed of an integrated operational amplifier is generally connected at the output. Since the input resistance of the op amp is generally higher, the discharge time of the capacitor is shorter. At the input end of the capacitor, an integrated operational amplifier can also be connected to take advantage of its smaller output resistance to speed up the charging time. In the selection of the switch, try to choose a switch with short switching time and relatively small aperture delay and aperture jitter, so as to ensure the performance index of the sample-and-hold capacitor and improve the sampling accuracy of the system. For the selection of holding capacitors, simulation design software should be used to analyze and design a variety of capacitance values to reach the compromise point of performance during sampling and holding, and to meet the design requirements of the system.